# Low Power RAM-Based Hierarchical CAM on FPGA

Ravvavarapu Chiranjeevi komal<sup>#1</sup>, Musala VenkateswaraRao<sup>\*2</sup> <sup>1</sup>Department of ECE, <sup>2</sup>Department of ECM KL University, Green Fields, Vaddeswaram, Guntur -522502, A.P, India <sup>1</sup> chiru.komal9@gmail.com <sup>2</sup> venkatvlsi@kluniversity.in

*Abstract-* In the Wireless routers and network devices like servers CAM Content-Addressable Memories will be mostly used as they have a good transmission rate to transfer the data packets. So the main role played by the CAM is it will easily transfer the internet packets like drop and forward mechanism. During such transmission CAM having a limitations like more power usage and less integration density, along with this CAM will not be accessible on the FPGA which will elaborate the usage of network framework. In order to reduce the high power consumption and to achieve more integration density, we proposed RAM based CAM in this paper. Now-a-days on modern FPGA we can see larger blocks of RAM.

Keywords- TCAM, Wireless routers, Power efficiency.

## I. INTRODUCTION

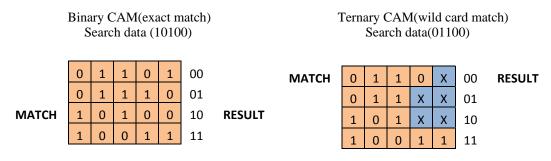

CAM is a type of special memory where it performs high speed search applications.In Existing random access memory (RAM), gives the user the address of the RAM returns data available for this specific job address. CAM about changing fashions .The key and came back to the address which is stored in memory. The of the cam which operate in a single clock cycle. It also works with high speed, and various other hardware and software applications systems today variable cam is used when it is necessary to divide, pick up and deliver packages. Two ternary CAM types. Binary CAM Binary means that only two logical bits 0 and 1, three times 0, 1, and X (timeless bit) cam. Take, for example stored in a "101XX" It complements the four keys or "10100", "10101", "10110", "10111" when multiple answers resembles the input data is important to encode should choose a special them. Table I shows the structure of TCAM inputs.

The size of the header, you need to consider several algorithms classification. Let matches exact specific examples of suitable recipient of the size or the prefix matching sets a sand numbers. The software algorithms, flexible and low productivity maintenance of hardware systems, are a binary cam used to determine the exact game where TCAM used to mitigate the range or add matches. TCAM widely used as a binary CAM thanks to its ability to minimum bit. Timeless centered TCAM. The integrated recommendations (ASIC) designed for a doll called native CAM. They native doll has a few limitations.

| Address | Ternary Data |   |   |     |     |   |   |   |  |

|---------|--------------|---|---|-----|-----|---|---|---|--|

|         | HP1          |   |   |     | HP2 |   |   |   |  |

| 0       | 0            | 0 | 0 | 0   | 1   | 0 | 1 | 0 |  |

| 1       | 0            | X | 0 | 1   | 0   | 0 | 1 | 0 |  |

| 2       | 1            | 0 | 0 | 1   | 1   | 0 | 0 | Х |  |

| 3       | 1            | Х | 1 | 0   | 1   | 0 | 0 | 0 |  |

|         | HP3          |   |   | HP4 |     |   |   |   |  |

| 4       | X            | 0 | 0 | 1   | 1   | 0 | 1 | 0 |  |

| 5       | 0            | 0 | 0 | 1   | 1   | 0 | 0 | 1 |  |

| 6       | 1            | 0 | 0 | 0   | 1   | 0 | 0 | 0 |  |

| 7       | 1            | 1 | 1 | 1   | 1   | 1 | 0 | 1 |  |

| TABLE I. | FONT   | SIZES | FOR | PAPERS   |

|----------|--------|-------|-----|----------|

| IADEE I. | 1 0141 | OILEO | POK | I AI EKS |

#### Fig.1.CAM vs TCAM

1. Since each bit required the match logic, the cost of per bit is high.

2. More Power consumption than RAMs due to match logic in every cell.

3.Native CAMs are absent in FPGA

Due to the above limitations, the more flexible and efficient method is required. RAM based CAM is introduced which gives the prominent technique among number of solutions. In this paper, we are proposing hierarchical finding techniques which will be more easy and high data rate transmission. In this technique, the entries are divided as high priorities such that priority entries are searched first is high priority. If the match doesnot found, then no further search will perform so, that the average power consumption is reduced.

## II. RAM-BASED TCAM EMULATION TECHNIQUES ON FPGA REVIEW

Xilinx and Altera have been proposed techniqued to design RAM based CAM on FPGA [3],[4].The Literature study of this topic can be found in [1][2].We have a formula N\*W TCAM,where N denotes number of TCAM words,W denotes width of each word.

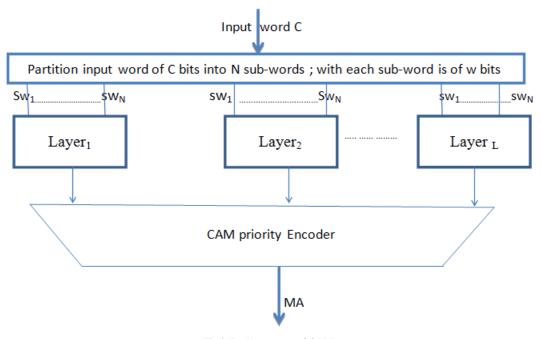

Fig.2. Basic structure of CAM

The main step of encoding preference to become the critical path. Several units of Fig.2 can be cascaded to form a processing architecture which is of parallel mechanism. Although [1] Jiang gave theoretical analysis W have TCAM \* N, where N the TCAM TCAM building Ramsay and word parallel and scalable W shows the number of terms for each word width figure, the proposed architecture, the optimization method is not required (2 ^ W) \* RAM Bits N to apply the same consumption Seeking. In his architecture, it is known for each block of the care and a hit or function, where w denotes the inlet valve that serves as the RAM addresses and the number of times each n-bit word size RAM. RAM requirement may be relaxed by dividing the key input W bit short in several key principles of equality, marked W. The total memory requirement

$$N * w = 2^w / w \tag{1}$$

In [1], the author observes and identifies an equation (1) is still a function of the memory requirements of minimally considered and W is obtained which is the smallest possible value such as 1 or 2. In fact, W generally have some value for a limited natural resources available. For example, the PGA is to use block RAMmemory W has a least value of 512, then if you are using distributed ram W has a minimum value of 32. The equation (1) means only a few small Ramsay equal depth used CAM application that requires less memory. However, each of the RAM word width depends on the specific application (for each word width corresponding to the depth of the RAM table CAM). Given the efficiency of the memory point, distributed RAM effectively block RAM implementation of TCAM because of its lower minimum depth. However, normally distributed RAM-memory has a small width and a large width is required by the application, a number of blocks allocated RAM should be connected in parallel. No matter what Ramsay used to apply TCAM

## III. PROPOSED METHODOLOGY FOR VARIOUS RAM BASED ARCHITECTURES FOR TCAM

Follow the model [1], but we will use the data so that data is always looking paramount. Moreover, the past game red light block (thing) is used for lease priority blocks the signal, which means that if the defense is not final match because research research and, therefore, consumption of average power is reduced.

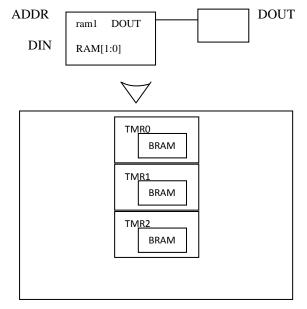

## A. An Architecture of RAM Memory Block

RAM-memory can be configured in various ways, such as a RAM FPGA port, dual RAM and easy access to the latest dual-port RAM, the current list is only available to some Simple dual-port RAM. The match signal to reverse the past and continues to low priority port, as shown in Figure

Fig.3. Basic RAM Architecture with I/O

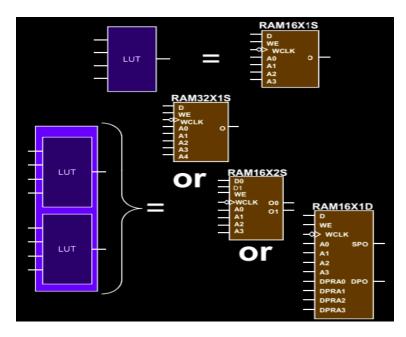

#### B. Distribution Architecture RAM

RAM lookup tables is to use a distributor is available in all rooms, and the minimum size of the RAM memory of the overall size of the LUT. There is a built-in power, distributed RAM, so as to use the clock gating techniques ON / OFF of the RAM, as shown in Fig.3.

Fig .4.Distribution Architecture RAM

## C. Parallel Architecture

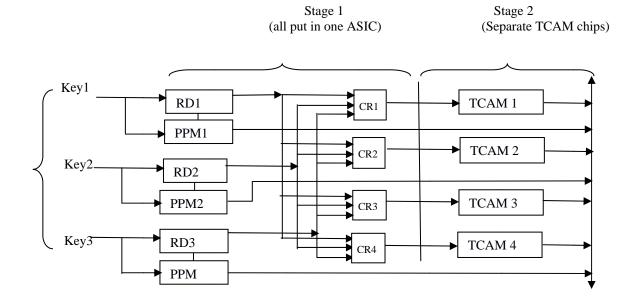

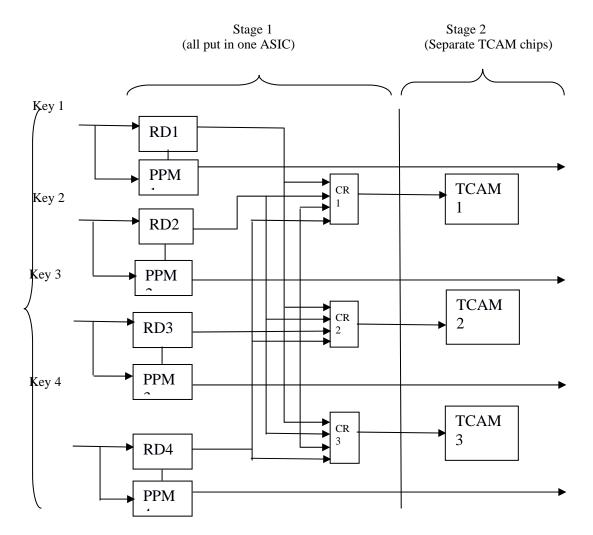

Recently, more and more space in the parallel architecture, and progress will be possible by simply adjusting the platform for a number of [8] students. detailed architecture of the parallel TCAM-based emulation RAM [1]. We changed the architecture of our planning process and seek hierarchical structure shown in Fig. 4. Note that the performance of this architecture can be improved with the addition of pipeline stages of said units and each unit. It takes more important encoder (omitted in the figure) for the final selection stage.

Fig.5. Parallel RAM- based Architecture

There are two types of RAM available FPGA block RAM and distributed. RAM blocks are often used to implement applications that require large amounts of memory capacity. distributor search RAM is to use tables (Lutz), which is available in all rooms. We conduct experiments Virtex6 XC6VLX75T Xilinx devices -3 degrees. We will publish the results on the basis of where and how the results of the Xilinx ISE 14.7. power. The results received from Xilinx Power Analyzer. In our experiments, we set the key input size 180-bit, if you select a line in figure 4, each tube of the device and the internal pipeline level for each unit. Each dual port RAM is configured in a port mode (SDP) and the second reading. While the other port RAM configurations are possible, for example, four doors are out of shape. In addition, we configure the width of each word, for example,72small.

## IV. SIMULATION ANALYSIS

## A. RAM-memory block Simulation

RAM FPGA Virtex6 each store up to 36Kb of small files which will be configured, 64Kb x 1 (block waterfall near 36 KB RAM), 1 x 32K, 16K x 2, 4 x 8 k, 4K x 2K x 9 18, 36 x 1 or 512 K x 72 simple dual-port mode. [5], to see the performance of the memory configuration of 512 x 72 experiments. If the draft 180-input bit support, RAM, 20 to a room. Virtex6 XC6VLX75T, 156 RAM. Therefore, it can be applied to the seventh level of target devices and the exact analysis is shown in below fig 5. Table II shows the simulation results.

| Block RAM Based<br>Architecture(7<br>stages,140/156 block RAMs) | Maximum<br>frequency (MHz) | Total power(watt) | Power saving Ratio |

|-----------------------------------------------------------------|----------------------------|-------------------|--------------------|

| With Hierarchical Searching                                     | 133                        | 2.548             | 11.0%              |

| Without Hierarchical<br>Searching                               | 133                        | 2.863             |                    |

| TABLE II. Architecture Analysis Block RAM-me | emory |

|----------------------------------------------|-------|

|----------------------------------------------|-------|

| Baseline ▼= 0<br>¶ Cursor-Baseline ▼= 1309.65ns |         |          | TimeA = 1309.65ns |          | Marker 2 = 1309.75ns |

|-------------------------------------------------|---------|----------|-------------------|----------|----------------------|

| Name <del>v</del>                               | Cursor▼ | òns      | 1309.65ns         | 1309.7ns | 1309.75ns 1309.      |

| ⊒ <b>)∄</b> DI[7:0]                             | 'h 00   | 00       |                   |          |                      |

| ±                                               | 'h 88   | 88       |                   |          | 53                   |

| ±                                               | 'h 001  | 000 (001 | <u>(</u> 000      |          |                      |

|                                                 | 1       |          |                   |          |                      |

|                                                 | 1       |          |                   |          |                      |

|                                                 | 0       |          |                   |          |                      |

|                                                 | 0       |          |                   |          |                      |

| ±                                               | 'h 0    | 0        |                   |          |                      |

|                                                 | 'h 000  | 000      |                   |          |                      |

|                                                 | 1       |          |                   |          |                      |

| wren                                            | 1       |          |                   |          |                      |

Fig: 6. Block RAM Architecture Analysis in Xlinix

# B. RAM distributed simulations

Creating FPGA resources referred to slide the two types of Xilinx FPGA sliced, cut, and cut. RAM distributed only supported on wedges. A piece of four LUTs and, when used in distributed RAM, various methods available in the dual port Wikipedia x 32 6 and 3 x 64 [6]. In our tests, we chose 6 x 32-bit memory bus as the base memory. This block is located in the iris (4-LUT). If the project is to support 180-bit key input, it takes 36 RAM. But we want them basics such as 72-bit block RAM (same plane). Therefore, the full 36 x 12 RAM for each basic unit. Virtex 6 XC6VLX75T can 16720 LUT used or shared RAM. Where each unit is 36 x 12 x 4 LUTs can be used up to nine levels of the target device. Table III shows the simulation results.

| Name           | Value |             | 505 ns  | 510 ns        | 515 ns              | 520 ns    | 525 ns         | 530 ns |

|----------------|-------|-------------|---------|---------------|---------------------|-----------|----------------|--------|

| lig ena        | 1     |             |         |               |                     |           |                |        |

| 🔓 clk          | í.    |             |         |               |                     |           |                |        |

| 🕨 駴 wea[0:0]   | 0     |             | 1       |               |                     |           | 0              |        |

| ▶ 📑 addra[7:0] | 10    | X 250 X 251 | 252 253 | 254 🗙 255 🗶 0 | $1 \times 2 \times$ | 3 X 4 X 5 | $X \in X = X$  | 8 (9)  |

| 🕨 駴 dina[7:0]  | 0     | 250 251     | 252 253 | 254 255       |                     |           | 0              |        |

| 🕨 駴 douta[7:0] | 10    |             | 0       |               | 1 2                 | 3 4 )     | <u>5 (6) 7</u> |        |

|                |       |             |         |               |                     |           |                |        |

|                |       |             | Reading | Data from B   | RAM                 |           |                |        |

|                |       |             |         |               |                     |           |                |        |

|                |       |             |         |               |                     |           |                |        |

Fig 7. Distributed RAM-based simulation analysis with Xlinix

TABLE III. Simulation analysis of Distributed RAM-based architecture

| Distributed RAM Based<br>Architecture(9<br>stages,15552/16720 LUTs) | Maximum<br>frequency (MHz) | Total power(watt) | Power saving<br>Ratio |

|---------------------------------------------------------------------|----------------------------|-------------------|-----------------------|

| With Hierarchical<br>Searching                                      | 109                        | 2.388             | 9.7%                  |

| Without Hierarchical<br>Searching                                   | 109                        | 2.643             |                       |

## V. CONCLUSION

In this article, we introduce technology RAM-based architecture TCAM energy optimization suitable for use in FPGAs. We would not affect Critical Path Timeline and maintain the same maximum frequency. The first results show the benefits of our approach. In the future it will be the formation of hierarchical update engine of our design process. One of the advantages of our approach is the most important risk areas and low divorced, and then upgrade to the target area has no effect on other sectors. Another aspect of the current situation will take this type of configuration RAM. For example, if you use -chaw quad-port RAM, a port for writing and three other ports to read. Since many ports for loading, performance may be improved.

#### REFERENCES

- [1] Open w-enabling innovatie in uwnetwerk. http://www.open w.org.

- [2] P. Bosshart, G. Gibb, H.-S. Kim, G. Varghese, N. McKeown, M. Izzard, F. Mujica, en M. Horowitz. Forwarding metamorfose: Fast programmeerbare match-actieverwerking in hardware voor SDN. In SIGCOMM '13: Proceedings of the ACM SIGCOMM 2013.

- [3] F. Baboescu, S. Singh, en G. Varghese. Pakketclassificatievoor core routers: Is ereenalternatiefvoor CAM? In INFOCOM '03: Proceedings van de jaarlijksegezamenlijkeconferentie van de IEEE Computer and Communications Societies, volume 1, pagina's 53-63, maart / april 2003 22.

- [4] W. Jiang "Scalable Ternary Content adresseerbaargeheugenImplementaties Met behulp van FPGA's" Naar ANCS '13: Proceedings of the ACM / IEEE Symposium over Architecturenvoor Networking and Communications Systems, pp 71-82, 2013.

- [5] C. A. Zerbini en J. M. Finochietto "Prestatie-evaluatie van pakketclassificatie op FPGA-gebaseerde TCAM emulatiearchitecturen" NaarGlobecom '12. Proceedings of the IEEE Global Communications Conference, pp 2766-2771, 2012..

- [6]

K.Locke.XAPP1151-Parametreerbare

Content-adresseerbaargeheugen.

2011.

http://www.xilinx.com/support/documentation/application notes / xapp1151 Param CAM.pdf.

2011.

- [7] Geavanceerde Synthesis Cookbook, Altera Corporation, San Jose, CA, july 2011. http://www.altera.com/literature/manual/stx\_cookbook.pdf

- [8] Virtex6 FPGA Memory Resources User Guide, Xilinx Inc 2014 http://www.xilinx.com/support/documentation/user\_guides/ug363.pdf

[9] Virtex6FPGAconfigureerbarelogischUserGuide, Xilinx Inc 2012

- http://www.xilinx.com/support/documentation/user\_guides/ug364.pdf.

[10] Z. Ullah, M. K. Jaiswal, Y. C. Chan en R. C. C.Cheung. "FPGA Implementatie van SRAM-gebaseerdeternaire Content adresseerbaargeheugen" Naar IPDPSW '12: Proceedings of the IEEE 26ste Internationaleparallelle en gedistribueerdeverwerking Symposium Workshops & PhD Forum 2012.

- [11] Z. Qian en M. Margala. "A Novel Low-Power en In-Place Split-Radix FFT processor," in GLVLSI'14: ACM Proc. van de 24ste Grote MerenSymp. op VLSI, Houston, TX, USA, 2014, pp.81-82

#### **AUTHOR PROFILE**

Ravvavarapu Chiranjeevi komal, was born on 25/09/1991. He received his B.Tech Degree in Electronics and Communication from Chalapathi Institute of Engineering and Technology, LAM, Guntur, Andhra Pradesh, INDIA in 2014.Presently he is Pursuing M.Tech in VLSI Specialization at KL University, Guntur, Andhra Pradesh, India. His main interest in Low power VLSI, Testing of VLSI circuits.

Musala VenkateswaraRao received the B.Sc degree in Electronics from Acharya Nagarjuna University, Guntur, India, in 2004, M.Sc. degree in Electronics from AcharyaNagarjuna University, Guntur, in 2006, the M.Tech degree in VLSI Design from Sathyabama University Chennai, in 2008 and Registered for Ph.D in KL University under VLSI. He is currently working as an Assistant Professor with K L University, Vaddeswaram. He is worked as an Assistant Professor in KIET Engineering College Korangi. Affiliated to JNT University Kakinada.His research interests are in the areas of Low power VLSI, VLSI Testing and MPSOC with particular interest in On-chip Trade off s for NoC(Network-on-Chip).