# **Current Conveyor Equivalent Circuits**

Tejmal S. Rathore<sup>1</sup> and Uday P. Khot<sup>2</sup>

<sup>1</sup>Electronics and Telecommunication Engineering Department, St. Francis Institute of Technology, Borivali (W), Mumbai 400 103, India. tsrathor@ee.iitb.ac.in <sup>2</sup>Electronics and Telecommunication Engineering Department, Thadomal Shahani Engineering College, Bandra (W), Mumbai 400 050, India.

upk@ee.iitb.ac.in

*Abstract*—An equivalence between a class of (current conveyor) CC II+ and CC II- circuits is established. CC IIequivalent circuit uses one extra element. However, under certain condition, the extra element can be eliminated. As an illustration of the application of this equivalence, minimal first and second order all-pass filters are derived. In certain cases, it is possible to compensate the effect of the input resistor of CC at port X. At the end, an open problem of realizing an *N*th order (N > 2) minimal all-pass filter is stated.

Keywards—Current conveyors, all-pass filters.

#### I. INTRODUCTION

Filters using current conveyors (CC) have become more attractive because of their wider bandwidth, lower power consumption and simpler circuitry in contrast to opamp-based filter circuits [1]. Recently, several CC-based first order all-pass filters have been reported [1-4]. In this paper, we present an equivalence between a class of CC II+ and CC II– circuits. From this equivalence, we have derived a set of minimal first and second order all-pass filters.

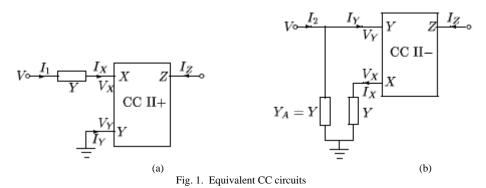

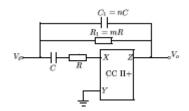

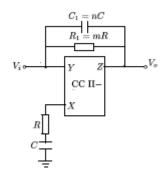

## II. CURRENT CONVEYOR EQUIVALENT CIRCUITS

Consider the circuits shown in Figs 1(a) and (b) where CC II has the characteristics  $V_X = V_Y$ ,  $I_Y = 0$ ,  $I_Z = I_X$ . For equivalence, the terminal behaviour of the two circuits should be identical, i.e., the voltage and the current at all the terminals of circuit shown in Fig. 1(a) should be identical to the corresponding terminals of the circuit shown in Fig. 1(b). Thus, for the same input voltage V, the input currents  $I_1$  in circuit shown in Fig. 1(a) should be equal to the input current  $I_2$  in circuit shown in Fig. 1(b). It can be seen that

$$I_1 = I_X = VY = I_2. (1)$$

Hence, the two circuits are equivalent.

Note that the equivalent circuit shown in Fig. 1(b) uses one extra element  $Y_A$ . However, if V happens to be a voltage of an ideal voltage source,  $Y_A$  become redundant and, therefore, can be eliminated. It may be noted that Y cannot assume a value  $\infty$  because, under this condition,  $V \rightarrow 0$ , and from (1), the current  $I_X$  will be indeterminate.

# III. APPLICATION OF THE CC EQUIVALENT CIRCUITS

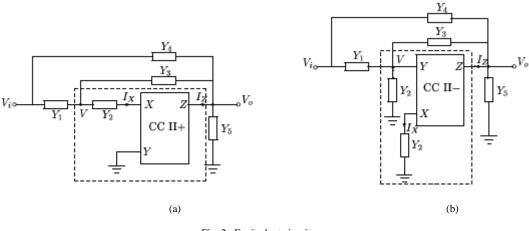

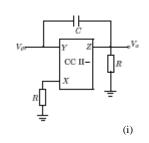

Consider the circuit shown in Fig. 2(a) and its equivalent shown in Fig. 2(b) obtained by replacing the dashed box.

Fig. 2. Equivalent circuits

Simple analysis of both circuits leads to the following relations.

$$I_X = I_Z = VY_2,\tag{2}$$

$$I_Z = (V - V_o)Y_3 + (V_i - V_o)Y_4 - V_oY_5$$

(3)

and

$$V = \frac{V_i Y_1 + V_o Y_3}{Y_1 + Y_2 + Y_3}.$$

(4)

From (2), (3), (4) we get,

$$T = \frac{V_o}{V_i} = \frac{Y_4(Y_1 + Y_2 + Y_3) + Y_1Y_3 - Y_1Y_2}{(Y_4 + Y_5)(Y_1 + Y_2 + Y_3) + Y_1Y_3 + 2Y_2Y_3}.$$

<sup>(5)</sup>

Thus, we see that the two circuits have the same voltage transfer function (VTF).

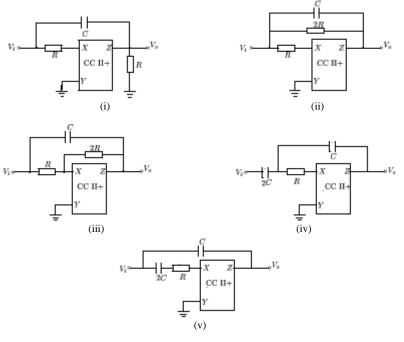

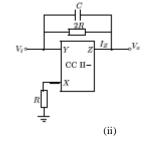

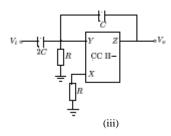

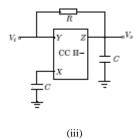

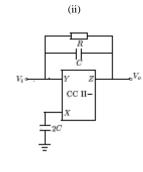

All ten possible<sup>1</sup> minimal<sup>2</sup> first order and one second order filter from (5) are obtained and shown in Fig. 3 and 4, respectively. Table I gives the elements for the first order all-pass filters given in Fig. 3 and Table II gives the elements for the second order filter given in Fig. 4.

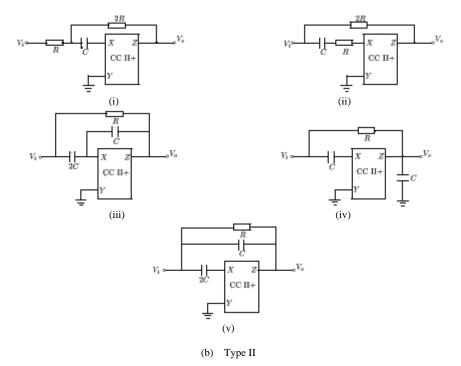

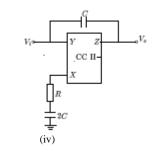

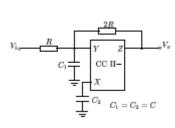

CC II– circuits shown in Fig. 5 are obtained from Figs 3(a)(i, ii, iv, v) and 3(b)(i, ii, iv, v) using the equivalence shown in Fig. 1. Since there is no Y in Figs 3(a)(iii) and (b)(iii), their CC II– equivalents do not exist. CC II– equivalent corresponding to Fig. 4 is shown in Fig. 6.

# IV. REMARKS

1. All the filters are classified into type I and II depending upon the sign of the transfer function, i.e.,

$$T = \frac{s - \omega_0}{s + \omega_0}$$

,  $T = -\frac{s - \omega_0}{s + \omega_0}$ , respectively. Thus, the circuits shown in Fig. 3(a) belong to Type I

and those shown in Fig. 3(b) belong to Type II.

- 2. Type I filters can be converted into type II by *RC*:*CR* transformation [5]. This is true for any *N*th order all-pass filter when *N* is odd. However, for *N* even, the sign of *T* remain unchanged.

- 3. All the first order filters of Figs 3 and 5 require 3 passive elements except that shown in Fig. 5(a)(iii) and 5(b)(i) which require 4 elements because *R* and *C* in these figures are not connected directly across an ideal voltage source. Only CC II– filters of Figs 5(b)(i, ii, iii) have all the capacitor(s) grounded. This situation is especially suitable for integrated circuit technology [6].

- 4. The analysis of the circuit shown in Fig. 4 leads to

<sup>&</sup>lt;sup>1</sup> see Appendix A

<sup>&</sup>lt;sup>2</sup> In the next section, it will be proved that 1C, 2R (2C, 1R) and one active element constitute a minimal first order all-pass realization.

$$T = \frac{s^2 - \frac{m - mn - 1}{mnCR}s + \frac{1}{mnC^2R^2}}{s^2 - \frac{mn + 1}{mnCR}s + \frac{1}{mnC^2R^2}}$$

(6)

Thus, the condition for realizing all-pass and notch filters are given in Table III.

Fig. 3. First order all-pass filters, G = 1/R

Fig. 4. Second order filter circuit using CC II+, G = 1/R

2R

CC II-

Х

R

$V_o$

(a) Type I

(iv)

(b) Type II

Fig. 5. CC II- equivalent first order all-pass filters

|              | $Y_1$    | $Y_2$    | $Y_3$ | $Y_4$ | $Y_5$ |

|--------------|----------|----------|-------|-------|-------|

| Fig $3a(i)$  | $\infty$ | G        | sC    | 0     | G     |

| Fig $3a(ii)$ | $\infty$ | G        | G/2   | sC    | 0     |

| Fig 3a(iii)  | G        | $\infty$ | G/2   | sC    | 0     |

| Fig $3a(iv)$ | sC       | G        | sC/2  | 0     | 0     |

| Fig $3a(v)$  | sC       | G        | 0     | sC/2  | 0     |

| Fig $3b(i)$  | G        | sC       | G/2   | 0     | 0     |

| Fig $3b(ii)$ | sC       | G        | 0     | G/2   | 0     |

| Fig 3b(iii)  | sC       | $\infty$ | sC/2  | G     | 0     |

| Fig $3b(iv)$ | sC       | $\infty$ | 0     | G     | sC    |

| Fig $3b(v)$  | $\infty$ | sC       | sC/2  | G     | 0     |

|              |          |          |       |       |       |

TABLE I

Elements for First Order All-Pass Filters given in Fig. 3

| TABLE II                                         |

|--------------------------------------------------|

| Elements for Second Order Filter given in Fig. 4 |

| $Y_1$ | $Y_2$ | $Y_3$ | $Y_4$                | $Y_5$ |

|-------|-------|-------|----------------------|-------|

| sC    | G     | 0     | $nsC + \frac{1}{m}G$ | 0     |

Fig. 6. CC II- equivalent second order filter

TABLE III Conditions for Realizing All-Pass and Notch

| all-pass | $m = \frac{2}{1-2n}, n < \frac{1}{2}$ |

|----------|---------------------------------------|

| notch    | $m = \frac{1}{1-n}, n < 1$            |

\_

The all-pass filter, for n=1/2, i.e., when  $m = R_1/R = \infty$ , or when  $R_1 = \infty$  (R = 0), reduces to first order all-pass filter shown in Fig. 3(a)(v) (Fig. 3(b)(v)). Similally, for n = 1, i.e., when  $m = \infty$  or when  $R_1 = \infty$  (R = 0) the notch filter reduces to a first order high (low) pass filter.

- 5. The effect of resistor  $r_X$  of CCs in Figs 3(a)(i, ii, iv, v), 3(b)(ii), 5(a)(i iv), 5(b)(ii), and Figs 4 and 6 can be compensated by reducing the value of the resistor *R* connected at terminal *X* by  $r_X$ [2].

- 6. Since  $V_X = V_Y$  in all the circuits, complementary transformation is applicable [7]. Hence, by interchanging the input and ground terminals, another VTF

$$T_1 = (1 - T) \tag{7}$$

can be obtained. Thus, by interchanging input and ground terminals of the type I (II) first order filters shown in Fig. 3 we get low (high) pass filters whereas, the second order all pass and notch filters shown in Figs 4 and 6 get converted into band-pass filters.

### V. MINIMAL NTH ORDER ALL-PASS REALIZATIONS

First order all-pass filter can be considered as a special case of

$$T' = (s - \frac{1}{\tau_1}) / (s + \frac{1}{\tau_2})$$

<sup>(8)</sup>

when  $\tau_1 = \tau_2$ . Since *T*' has a positive real zero, it can not be realized with only passive elements [8]. Thus, at least one active element is required. Further, since *T*' is of first order, at least one capacitor is required. Finally, since  $\tau_{1,2}$  have the dimensions of time, they must represent two different *RC* products, and therefore, at least one capacitor (resistor) and two resistors (capacitors) are required to give  $\tau_{1,2} = CR_{1,2} (C_{1,2}R)$ . Thus, 1*C*, 2*R* (2*C*, 1*R*) and one active element constitute the minimal realization of *T*'. Since,  $\tau_1 = \tau_2$  in (8) does not reduce the number of internal critical frequencies of *T*', the same number of passive and active elements also constitute the minimal realization of *T*. Therefore, all the first order all-pass filters shown in Figs 3 and 5, except that shown in Figs 5(a)(ii) and 5(b)(i), are minimal. Similarly, it can be shown that *N* capacitors, 2 resistors and one active element will constitute an *N*th order minimal realization. Hence, the second order filters shown in Figs 4 and 6 are also minimal. However, higher order minimal all-pass filters are perhaps not known and need to be searched.

#### VI. CONCLUSIONS

The equivalence between the current conveyor circuits shown in Fig. 1 has been established. From these equivalent circuits as many as 8 minimal first order single capacitor all-pass filters and 2 minimal second order all-pass and notch filters have been derived. It has been shown that NC, 2R and 1 active element constitute a minimal Nth order realization. Such realizations for N > 2 are not known and need to be searched.

## REFERENCES

- [1] B. Wilson, "Recent developments in current conveyors and current-mode circuits," IEE Proceedings, vol. 137, no. 2, pp. 63-77, 1990.

- [2] A. Toker, S. Ozcan, H. Kuntman, and O. Cicekoglu, "Supplementary all-pass sections with reduced number of passive elements using a single current conveyor," *Int. J. Electron.*, vol. 88, no. 9, pp. 969-976, 2001.

- [3] I. A. Khan and S. Maheshwari, "Simple first order all-pass section using a single CCII," Int. J. Electron., vol. 87, no. 3, pp. 303-306, 2000.

- [4] O. Cicekoglu, H. Kuntman, and S. Berk, "All-pass filters using a single current conveyor," Int. J. Electron., vol. 86, no. 8, pp. 947-955, 1999.

- [5] S. K. Mitra, Analysis of Linear Active Networks, John Wiley & Sons, Inc., New York, 1968.

- [6] M. Bhushan, R W Newcomb, "Grounding of capacitors in integrated circuits," *Electronics Letters*, vol. 3, pp. 143-149, 1967.

- [7] T. S. Rathore, "Complemetary transformation," IEEE Trans., vol. CAS-27, pp. 57-59, 1980.

- [8] S. Seshu and M. B. Reed, Linear Graphs and Electrical Networks, (Reading : Mass. Addison-Wesley), 1961.

#### APPENDIX A

It has been shown that three elements are required for minimal realization of a first order all-pass filter. Thus, 3 out of 5 elements in Fig. 2 are to be chosen as passive elements and the remaining two could be any one of the four combinations (0, 0),  $(0, \infty)$ ,  $(\infty, 0)$ ,  $(\infty, \infty)$ . There will be in all  ${}^{5}C_{3} = 10$  combinations of 3 passive elements. However, it is found that 3 combinations give trivial circuits which are not all-pass in nature. Further, out of the 4 combinations of the other 2 elements, only 1 gives the non-trivial circuit in each of the above 7 combinations. Thus, there are only 7 combinations of 3 element circuits. These 3 elements may be either 1*C* and 2*R* or 2*C* and 1*R* for minimal realization, thus giving a total of 6 circuits in each of the 7 combinations. However, out of 42 cases, only 18 yield the non-trivial all-pass filters. Out of these, only 10 possible distinct topologies result. These are listed in Table I and shown in Fig. 3.

#### AUTHORS PROFILE

T S Rathore was born in Jhabhua (M P, India) on Oct. 29, 1943. He received the B Sc (Electrical Engineering), M E (Applied Electronics & Servomechanisms), and Ph D (by research on Passive and Active Circuits) degrees in Electrical Engineering from Indore University, Indore, India in 1965, 1970 and 1975, respectively.

He served SGSITS, Indore from 1965 to 1978 before joining the EE Department of IIT Bombay from where he retired as a Professor on superannuation in June 2006. Currently, from July 2006, he is the Dean (R&D) and Head of Electronics & Telecommunication Department at St. Francis Institute of Technology, Borivali.

and a visiting researcher at the University of South Australia, Adelaide (March-June 1993). He was an ISTE

visiting professor (2005-2007). He has published and presented over 200 research papers in various national/international journals and conferences. He has authored the book Digital Measurement Techniques, New Delhi: Narosa Publishing House, 1996 and Alpha Science International Pvt. Ltd., U K, 2003 and translated in Russian language in 2004. He was the Guest Editor of the special issue of Journal of IE on Instrumentation Electronics (1992). He is a member on the editorial boards of ISTE National Journal of Technical Education and IETE Journal of Education. He has witnessed, organized and chaired many national/international conferences and in some he was also the Chief Editor of the proceedings.

His areas of teaching and research interest are Analysis and Synthesis of Networks, Electronic Circuit Design, Switched-Capacitor Filters, Electronic-Aided Instrumentation, Hartley Transform, Signal Processing, Fault Diagnosis and Knowledge-Based Systems.

Prof. Rathore is a Senior Member of IEEE (USA), Fellow of IETE (India), Fellow of IE (India), Member of ISTE (India), Member of Istrument Society of India, Member of Computer Society of India. He has been listed in Asia's Who's Who of Men and Women of achievement (1991). He has played a very active role as Fellow of IETE and has served its Mumbai Centre as Volunteer member (1997-98), Co-opted member (1998-99), Secretary (1999-2001), Chairman (2001-02), Vice Chairman (2003-06) and Chairman (2006-08).

He has received IETE M N Saha Memorial Award (1995), IEEE Silver Jubilee Medal (2001), ISTE U P Government National Award (2002), ISTE Maharashtra State National Award (2003), IETE Prof S V C Aiya Memorial Award (2004), IETE BR Batra Memorial Award (2005), IETE Prof K Sreenivasan Memorial Award (2005). IETE K S Krishnan Memorial Award (2009), IETE - Hari Ramji Toshniwal Gold Medal Award (2010), and IETE best paper award published in IETE J of Education (2011).

Uday P Khot was born in Kolhapur (MS) on June 15, 1970. He obtained B. E. (Ind. Electronics) from Amaravati University in 1991 and M. Tech. (Control and Instrumentation) from IIT Bombay in 1999 and Ph D (by research on Synthesis of Analog Circuits Employing Current-Mode Building Blocks) in Electrical Engineering from IIT Bombay, India in January 2010.

He served Bharati Vidyapeet's Institute of Technology, Navi Mumbai from 1992 – 1999 as a lecturer and Thadomal Shahani Engineering College, Mumbai, as an Assistant Professor from 1999 – 2006. He is an Associate Professor since January 2006. From January 2010, he is the Head of Electronics & Telecommunication Department at Thadomal Shahani Engineering College, Mumbai.

Dr Khot is a Fellow Member of IETE (India), Member of ISTE (India), Member of IEEE (USA) and Member of IE (India). He has been listed in the International Who's Who of Professionals Historical Society having demonstrated exemplary achievement and distinguished contributions to the business community, edition 2010-2011. He has served IETE Mumbai Centre as a Member (2004-2008).

He has published more than 20 research papers in National/International journals and conferences. His areas of research interest are: Synthesis of analog current-mode circuits, fault diagnosis in analog/digital circuits, and microwave circuits.