# Full-Wave Rectifier Circuit Responding in Linear Wide Range by Two Stage CMOS

Theerayut Janjaem<sup>#2</sup> Bancha Burapattanasiri<sup>#1, 3</sup> and Sanchaiya Pasomkusolsil<sup>#2</sup>

<sup>#1</sup>Department of Electronic and Telecommunication Engineering, Faculty of Engineering, K.B.U., Bangkok, Thailand 10250

<sup>#2</sup>Department of Electrical Engineering, Faculty of Engineering, K.B.U., Bangkok, Thailand 10250

<sup>#3</sup>Engineering Collaborative Research Center, Faculty of Engineering, K.B.U., Bangkok, Thailand 10250

bancha\_bu@eng.kbu.ac.th

Abstract—This article is present full-wave rectifier circuit responding in linear wide range by two stage CMOS by 0.5  $\mu$ m CMOS technology,  $\pm$  1.5 V low voltage, operation input receiver and output current mode, it responded operational at high frequency. The components of structure circuit are two stage CMOS circuit and current mirror circuit. The performances of the proposed circuit are investigated through PSpice. They show that the proposed circuit can function as maximum input current ranges 300  $\mu$ A<sub>p-p</sub>, responding at maximum frequency ranges 10 MHz, high precision, low power, non precision zero-crossing output signal, and uses a little of transistors. Furthermore, the circuit is able to generate square signal, it is operating at voltage mode but without modification or elaboration to structure of circuit.

# I. INTRODUCTION

Full-wave rectifier circuit is very importance in analog signal processing, such as AC voltmeter, detector signal circuit, demodulate circuit, etc. [1]-[2]. So it always has development in full-wave rectifier circuit. For example full-wave rectifier circuit in voltage mode [3], full-wave rectifier circuit in diode and bipolar transistor [4]. It has to use the threshold voltage 0.3 volt for germanium (Ge) and 0.6 volt for silicon (Si). Therefore, it has unstable signal in crossing zero and in this low input signal case. The circuit, it unable to working, because of diode and transistor characteristics are limit. This limitation is improved by designing, they unused diode and bipolar transistor, but they use other active device. In the past century they have a lot of presentation, who has presented full-wave rectifier circuit in current mode, but the circuit still have complicated of device, thus it have complicated in working and dissipation of current source too. So, in this article we would like to show a new choice of full-wave rectifier circuit, it easier to understand and uncomplicated in compound with active device, but still have high quality of working function with CMOS technology. The CMOS technology has compound with two stage CMOS, it still has translinear and current mirror circuit put together, and then it able to responding in wide linear, working at high frequency, responding at high input precision signal, low losing power and uses a little of transistor.

#### **II. FUNCTIONAL**

# A. Translinear circuit

From the presented show translinear is the main device,

thus should to know about the functional of translinear circuit, and then can be written the relation of voltage and within resistance as fig. 1

Fig. 1. (a) Equivalent circuit and (b) Basic translinear circuit

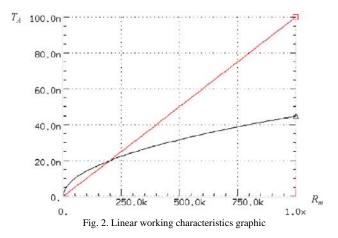

Designing of circuit is necessary to know about the inductive resistance within alternating current. For still have translinear characteristics, and use to apply working in current comparator circuit as fig. 2 [5].

Generally, in considering we are interested in impedance it able to see from fig. 1 (a). When  $R_a$  and  $C_a$  parallel compound at input with basic translinear equivalent circuit, after that the working stage is chance and the best working stage able to find out from  $R_a$  and  $R_b$  as equation (1) should to setting  $C_a$  equal to  $C_b$ .

$$v_{o}(t) = g_{m}R_{a}R_{b}J\left(1 - \frac{\tau_{a}}{\tau_{a} - \tau_{b}}e^{-\frac{t}{\tau_{a}}} - \frac{\tau_{a}}{\tau_{b} - \tau_{a}}e^{-\frac{t}{\tau_{b}}}\right), t > 0 \quad (1)$$

# B. Completely full-wave rectifier circuit responding in linear wide range by two stage CMOS.

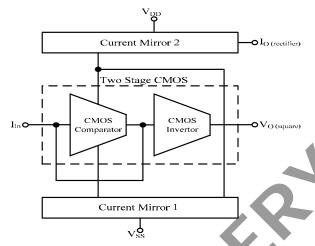

From the principle of translinear circuit, when it used to designing in two stage CMOS circuit and current mirror circuit combined with together after that it able to see the structure of completely full-wave rectifier circuit responding in linear wide range by two stage CMOS as diagram block fig. 3

Fig. 3. Diagram full-wave rectifier circuit responding in linear wide range by two stage CMOS

So, the structure it will combine with three part of circuit, first the CMOS current comparator circuit, second the CMOS inverter circuit, and third the current mirror circuit. For the functional, when the CMOS current comparator circuit received input positive and negative, it will starting to compare the circuit by bring negative signal passing to the current mirror circuit 2, and positive signal passing to the current mirror circuit 1. The both of signal, they will be combined with together at input current mirror circuit 2, after that the new signal is full-wave output signal. At the same time positive and negative signal from the CMOS current comparator circuit it has passed to CMOS inverter, after that new signal is output square working in voltage.

$$I_{DM2} = 0$$

and  $I_{DM1} = -I_{in}$  then  $I_{in} > 0$

$$I_{DM1} = 0$$

and  $I_{DM2} = I_{in}$  then  $I_{in} < 0$  (3)

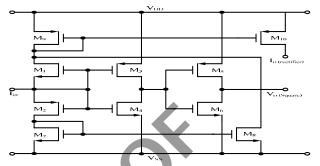

From the fig. 4 completely full-wave rectifier circuit responding in linear wide range by two stage CMOS, when sending input signal as equation (2) after that  $M_1$ ,  $M_4$  transistor able to flowing, but  $M_2$ ,  $M_3$  transistor unable to flowing. Thus,  $I_{dm1}$  equivalent to  $-I_{in}$  and inversion input signal is less than zero it will make  $M_2$ ,  $M_3$  transistor able to flowing and  $M_1$ ,  $M_4$  transistor unable to flowing, thus  $I_{dm2}$  equivalent to  $I_{in}$  as equation (3)

Fig. 4. Completely full-wave rectifier circuit responding in linear wide range by two stage CMOS

While,  $M_1$  and  $M_2$  transistor are flowing,  $V_{SS}$  and  $V_{DD}$  voltage are sending to  $M_7$ ,  $M_8$ ,  $M_9$  and  $M_{10}$  transistor. After that  $M_7$  transistor is flowing and it have reflected to  $M_8$  transistor drain pin. For combine with  $M_9$  transistor drain pin, and then it will mirror current passing to  $M_{10}$  transistor drain pin, after that appear full-wave signal in current mode at output as equation (4).

$$I_{out(rectifier)} = I_{DM8} + I_{DM9} = I_{DM10}$$

(4)

$$I_{t(sauare)} = V_{ss}$$

then  $I_{in} > 0$  and  $V_{out(sauare)} = V_{DD}$  then  $I_{in} < 0$  (5)

At the same time,  $I_{in}$  current signal from equation (2) and (3) it will sending back to input CMOS inverter. Thus,  $M_5$  and  $M_6$  switching to flow after that square signal circuit source working in voltage mode at  $M_5$  and  $M_6$  transistor drain pin as equation (5)

### III. THE SIMULATION RESULT QUALITY OF WORKING

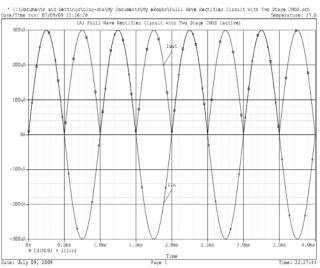

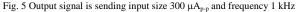

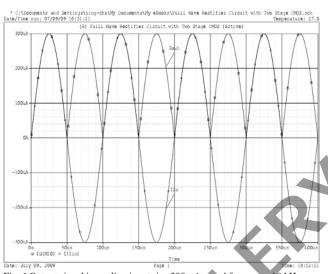

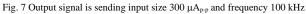

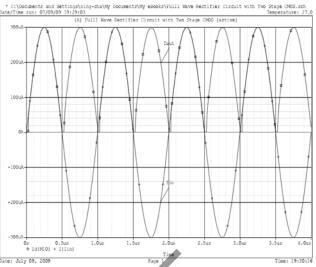

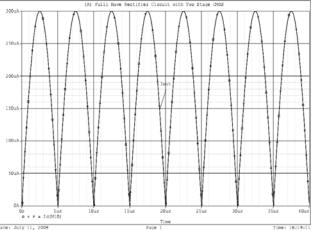

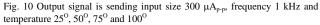

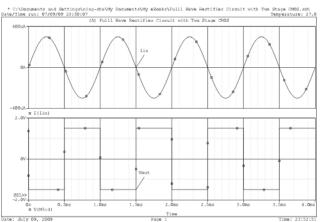

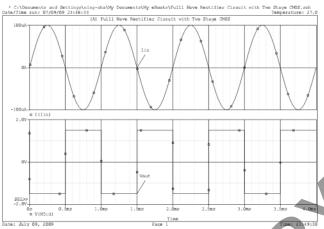

For confirmation about the performance of circuit, therefore uses PSpice program in the simulation. Setting parameter 0.5  $\mu$ m of MOSIS for transistor PMOS and NMOS V<sub>DD</sub> = 1.5 V V<sub>SS</sub> = -1.5V. Input current working at range 0-300  $\mu$ A<sub>p-p</sub>. Fig. 5 output signal is sending input size 300  $\mu$ A<sub>p-p</sub> and frequency 1 kHz. Fig. 6 output signal is sending input size 300  $\mu$ A<sub>p-p</sub> and frequency 10 kHz. Fig. 7 output signal is sending input size 300  $\mu$ A<sub>p-p</sub> and frequency 10 kHz. Fig. 7 output signal is sending input size 300  $\mu$ A<sub>p-p</sub> and frequency 10 kHz. Fig. 8 output signal is sending input size 300  $\mu$ A<sub>p-p</sub> and frequency 10 kHz. Fig. 8 output signal is sending input size 300  $\mu$ A<sub>p-p</sub> and frequency 1 MHz. Fig. 9 output signal is sending input size 300  $\mu$ A<sub>p-p</sub> and frequency 1 kHz. Fig. 10 output signal is sending input size 300  $\mu$ A<sub>p-p</sub> and trequency 1 kHz and temperature 25<sup>o</sup>, 50<sup>o</sup>,75<sup>o</sup> and 100<sup>o</sup>. Fig. 11 output square signal is sending input size 300  $\mu$ A<sub>p-p</sub> and frequency 1 kHz. Fig. 12 output square signal is sending input size 300  $\mu$ A<sub>p-p</sub> and frequency 1 kHz.

(2)

# Bancha Burapattanasiri et al /International Journal of Engineering and Technology Vol.1(2), 2009, 46-49

Fig. 9 Output signal is sending input size 300  $\mu A_{\text{p-p}}$  and frequency 10 MHz

Fig. 11 Output square signal is sending input size 100  $\mu A_{p\text{-}p}$  and frequency 1 kHz

Fig. 12 Output square signal is sending input size 300 µA<sub>p-p</sub> and frequency 1 kHz

# IV. CONCLUSION

The presented circuit is compound a little of transistor, noncomplex working function, reduce wastage of current source, working at input current mode, output is full-wave signal current mode and square signal voltage responding in linear wide range by low voltage at  $\pm$  1.5 V. From the simulation is able to confirm the quality of working at maximum frequency 10 MHz, maximum output 300 µA<sub>p-p</sub>, losses power 198 pW and insensitive from temperature, thus it suitable to development in integrated circuit and application in analog signal processing field.

#### ACKNOWLEDGMENT

The researchers, we are thank you very much to our parents, who has supporting everything to us. Thankfully to all of professor for knowledge and a consultant, thank you to Miss Suphansa Kansa-Ard for her time and supporting to this research. The last one we couldn't forget that is Kasem Bundit University, Engineering Faculty for supporting and give opportunity to our to development in knowledge and research, so we are special thanks for everything.

#### REFERENCES

- Barker, R.W.J., "Versatile precision full wave Rectifier," Electron Letts, [1] 5: Vol.13, pp. 143-144, 1977.

- Barker, R.W.J. and Hart, B.L., "Precision absolute-value circuit [2] technique," Int. J. Electronics Letts, 3: Vol.66, pp. 445-448, 1989.

- Toumazou, C. and Lidgey, F.J., "Wide-Band precision rectification," [3] IEE Proc. G, 1: Vol.134, pp.7-15, 1987.

- [4] Wang, Z., "Full-wave precision rectification that is performed in current domain and very suitable for CMOS implementation," IEEE Trans. Circuits and Syst, 6: Part I, Vol. 39, pp.456-462, 1992.

- A. Rodrigues-Vazquez, R. Dominquez-Castro, F. Medeiro and [5] M. Delgado-Restituto, "High Resolution CMOS Current Comparators: Design and Applications to Current-mode Function Generation I," Analog Integrated Circuit and Signal Processing, Vol.7 (Special Issue on Current-Mode Circuit), pp. 149-165, Kluwer March 1995.

- [6] A. Monpapassorn, K. Dejhan, and F.Cheevasuvit, "CMOS dual output current mode half-wave rectifier," International Journal of Electronics, Vol. 88, 2001, pp. 1073-1084.

- Toumazou, C., Lidgey, F.J.and Chattong, S., "High frequency current [7] conveyor precision full-wave rectifier," Electron. Letts, 10: Vol. 30, pp. 745-746, 1994.

- [8] Wilson, B. and Mannama, V., "Current-mode rectifier with improved precision," Electron. Letts, 4: Vol. 31, pp. 247-248, 1995. Surakampontorn, W. and Riewruja, V., "Integrable CMOS sinusoidal

- [9] frequency doubler and full-wave rectifier," Int.J. Electronics, Letts, 3: Vol. 73, pp. 627-632, 1992.

- [10] Traff, H., "Novel Approach to High Speed CMOS Current Comparators," Electron, Letts, 3: Vol. 28, pp. 310-312, 1992. Monpapassorn, A., "Improved Class AB Full-Wave rectifier,"

- Thammasat Int. J. Sc. Tech., No. 3, November, Vol. 4, 1999.

### **ABOUT THE AUTHORS**

Mr.Bancha Burapattanasiri received the bleacher degree in electronic engineering from Kasem Bundit University in 2002 and master degree in Telecommunication Engineering, from King Mongkut's Institute of Technology Ladkrabang in 2008. He is a Electronic Telecommunication lecture of and Engineering, Faculty of Engineering, Kasem Bundit University, Bangkok, Thailand. His research interests analog circuit design, low voltage, high frequency and high-speed CMOS

technology.

Mr.Sanchaiva Pasomkusolsil received the master degree in Telecommunication Engineering, from King Mongkut's Institute of Technology Ladkrabang in 2006. He is a lecture of Electrical Engineering Faculty of Engineering, Kasem Bundit University, Bangkok, Thailand. His research interests are harmonic analysis, energy & power system, high voltage engineering and electrical machines.

Mr.Theerayut Janjaem received the master degree in Telecommunication Engineering, from King Mongkut's Institute of Technology Ladkrabang in 2005. He is a lecture of Electrical Engineering Faculty of Engineering, Kasem Bundit University, Bangkok, Thailand. His research interests are energy, analog circuit design, low voltage, high frequency and high-speed CMOS technology.